逻辑门电路

字数

749 字

阅读时间

3 分钟

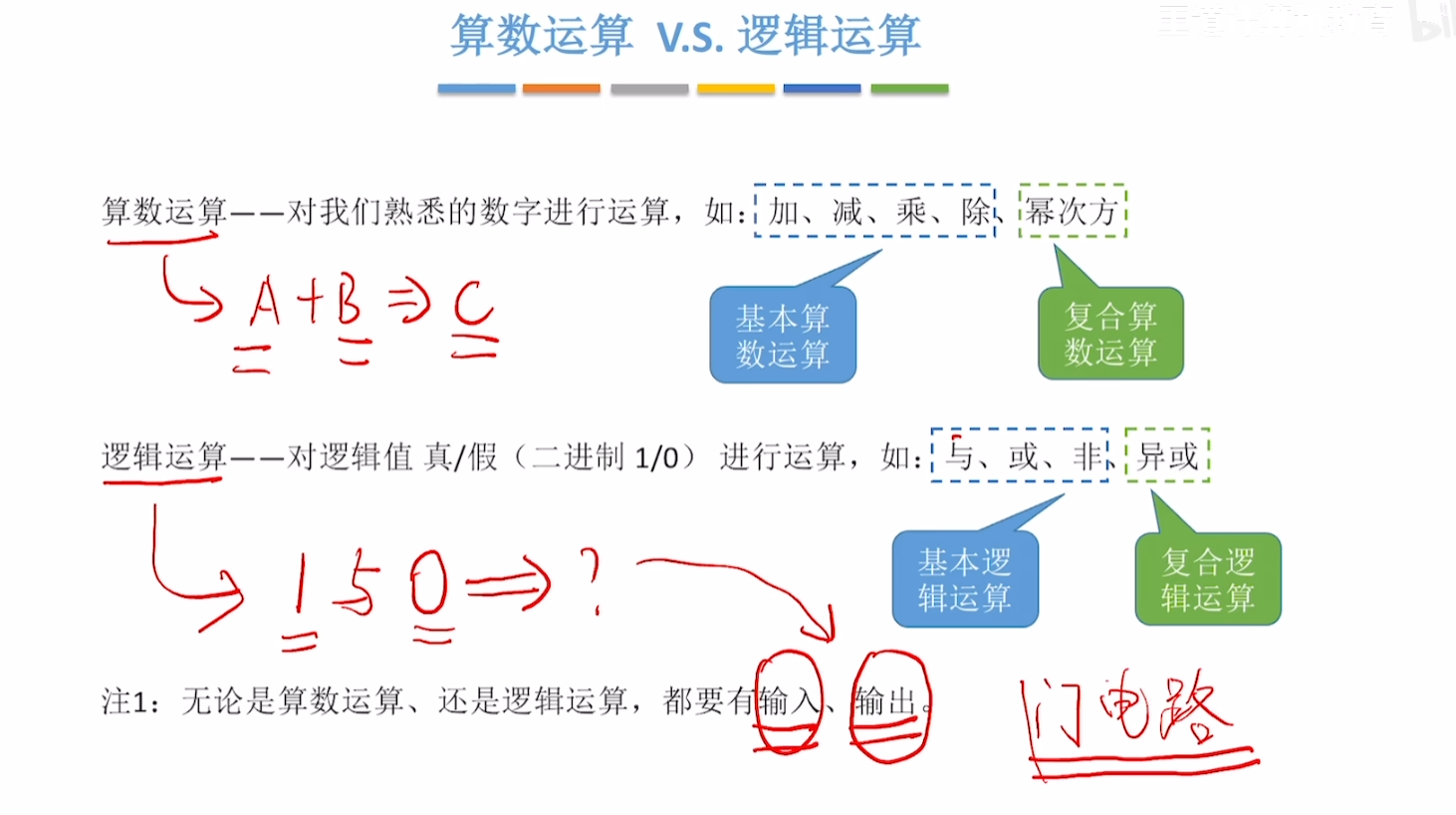

基本运算逻辑

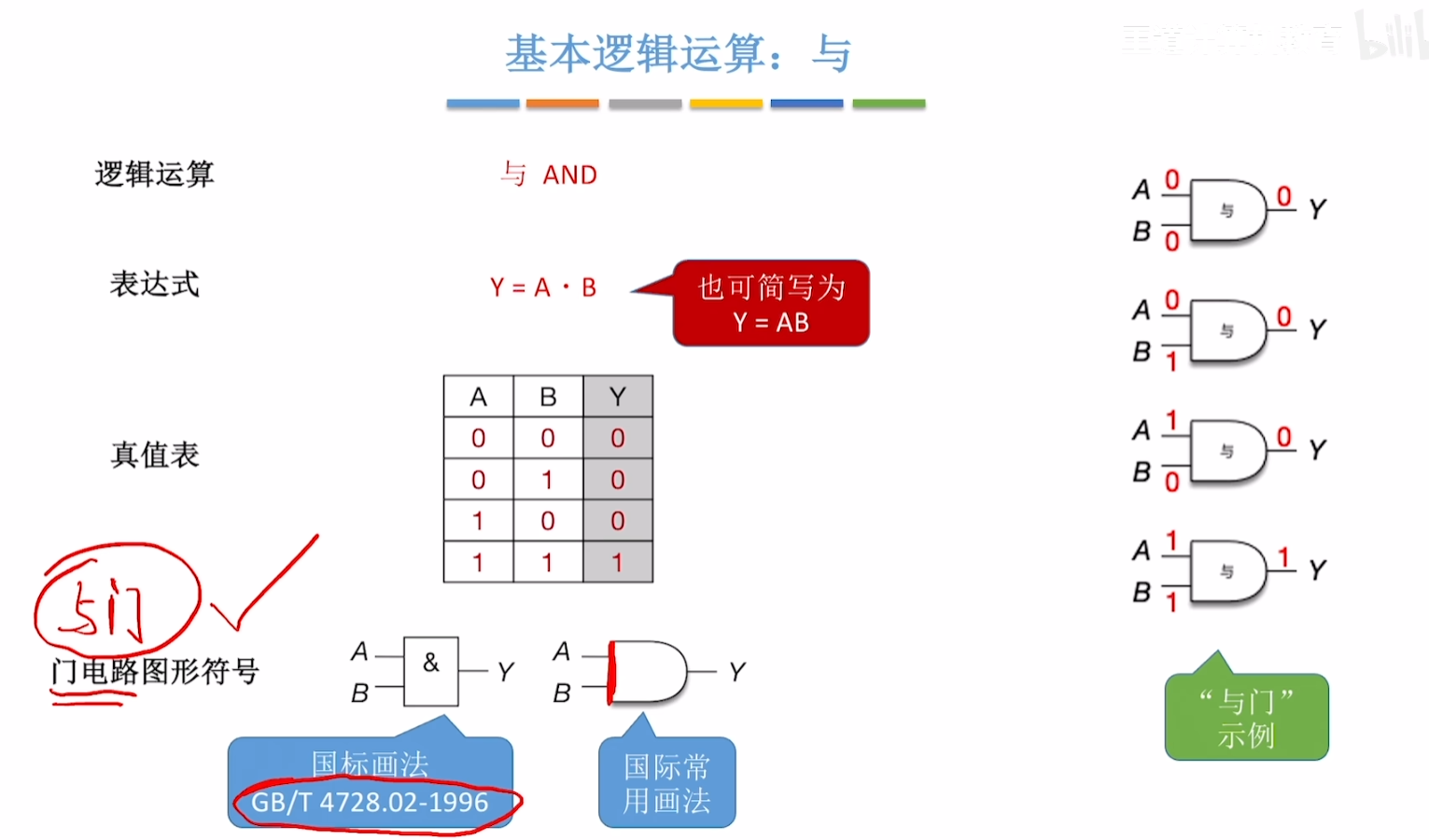

与运算

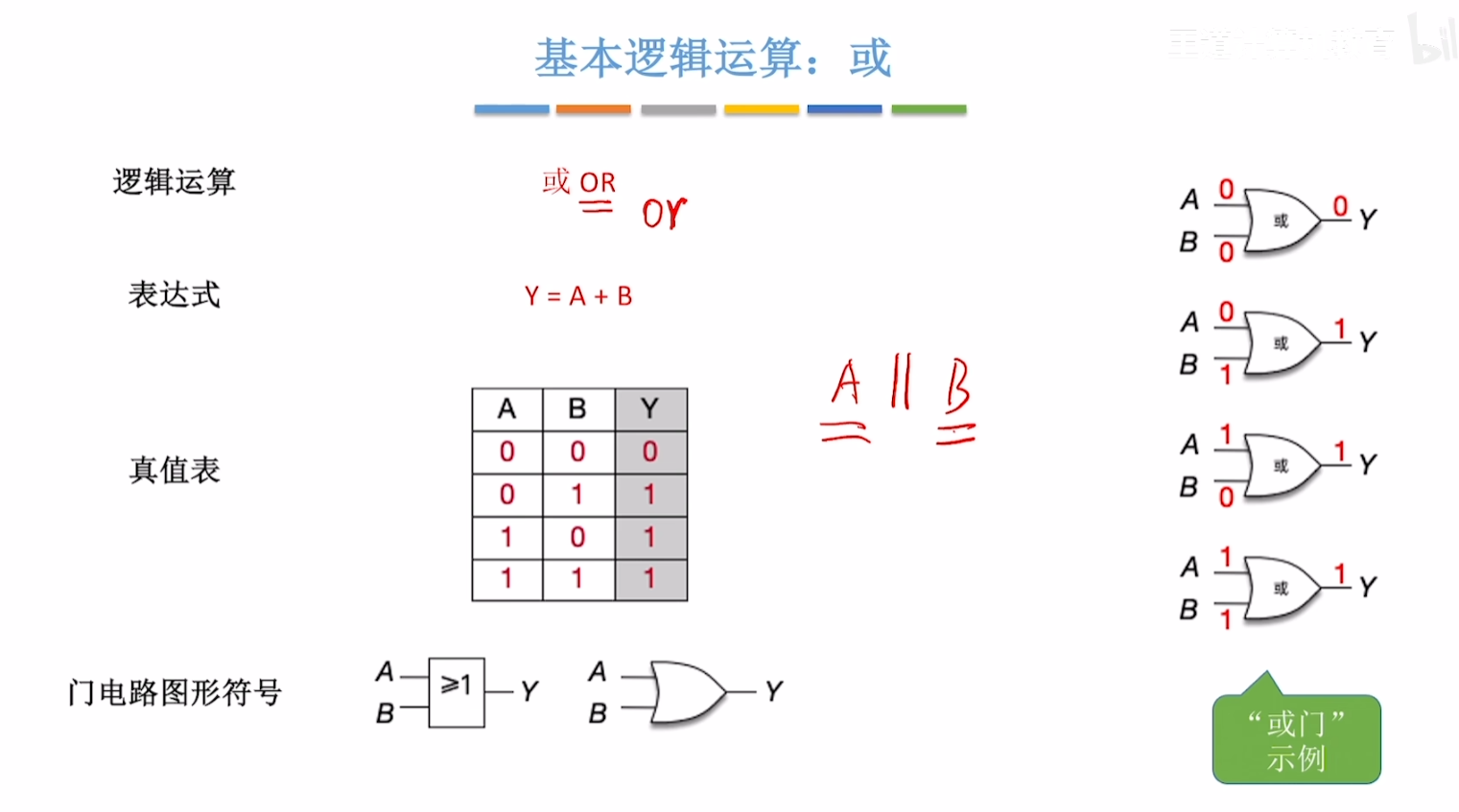

或运算

重点关注右边的国际画法

重点关注右边的国际画法

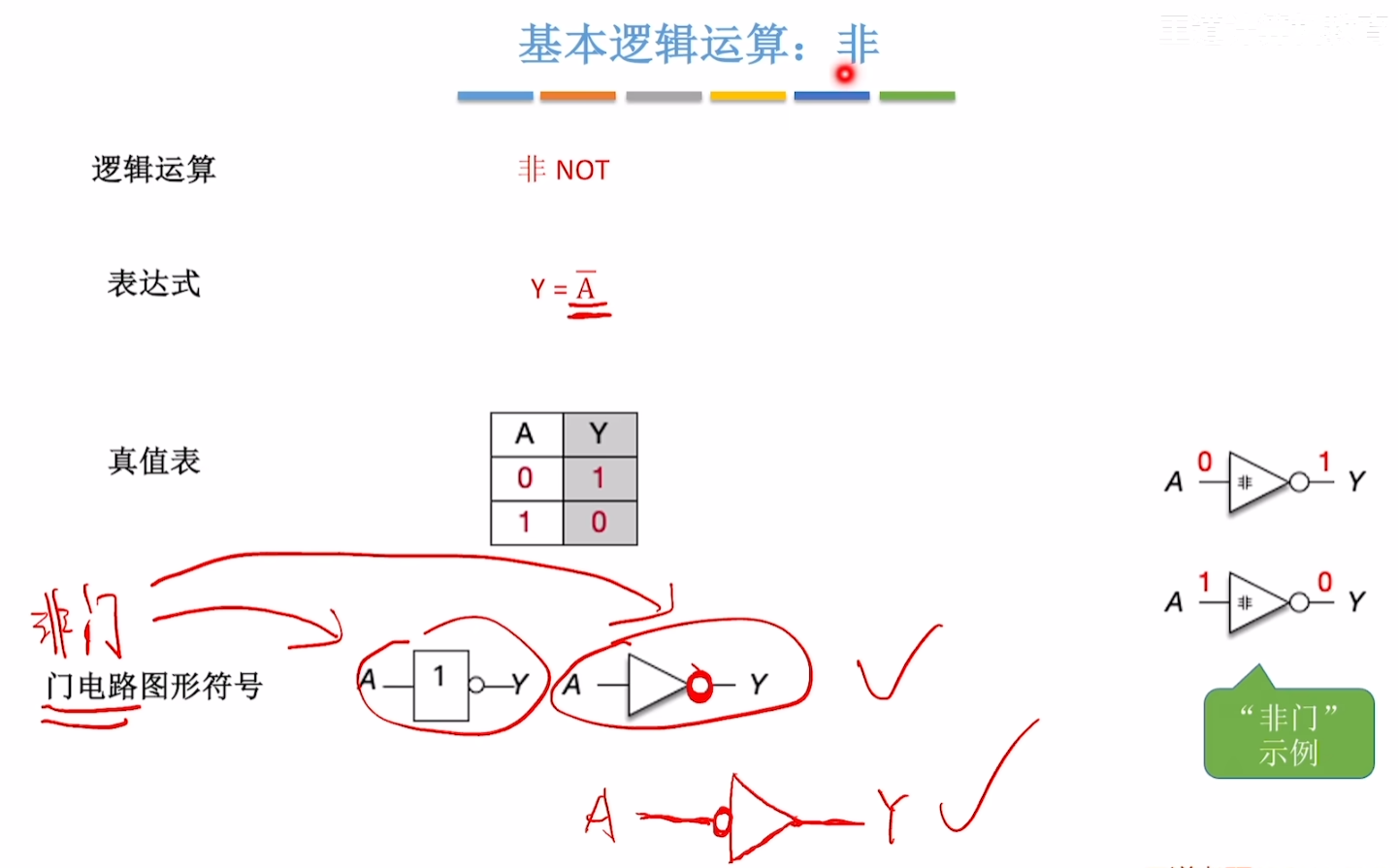

非运算

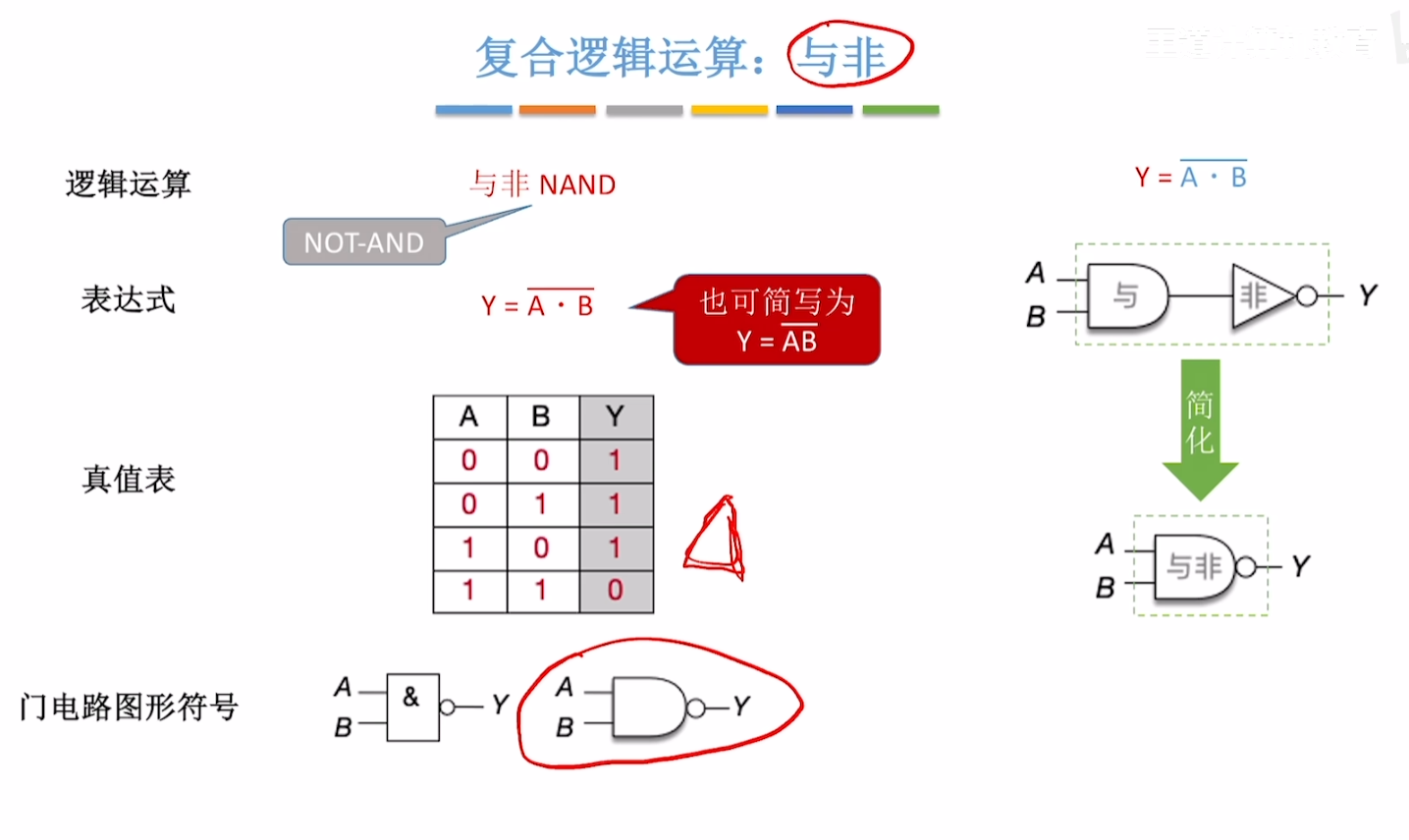

与非门逻辑运算

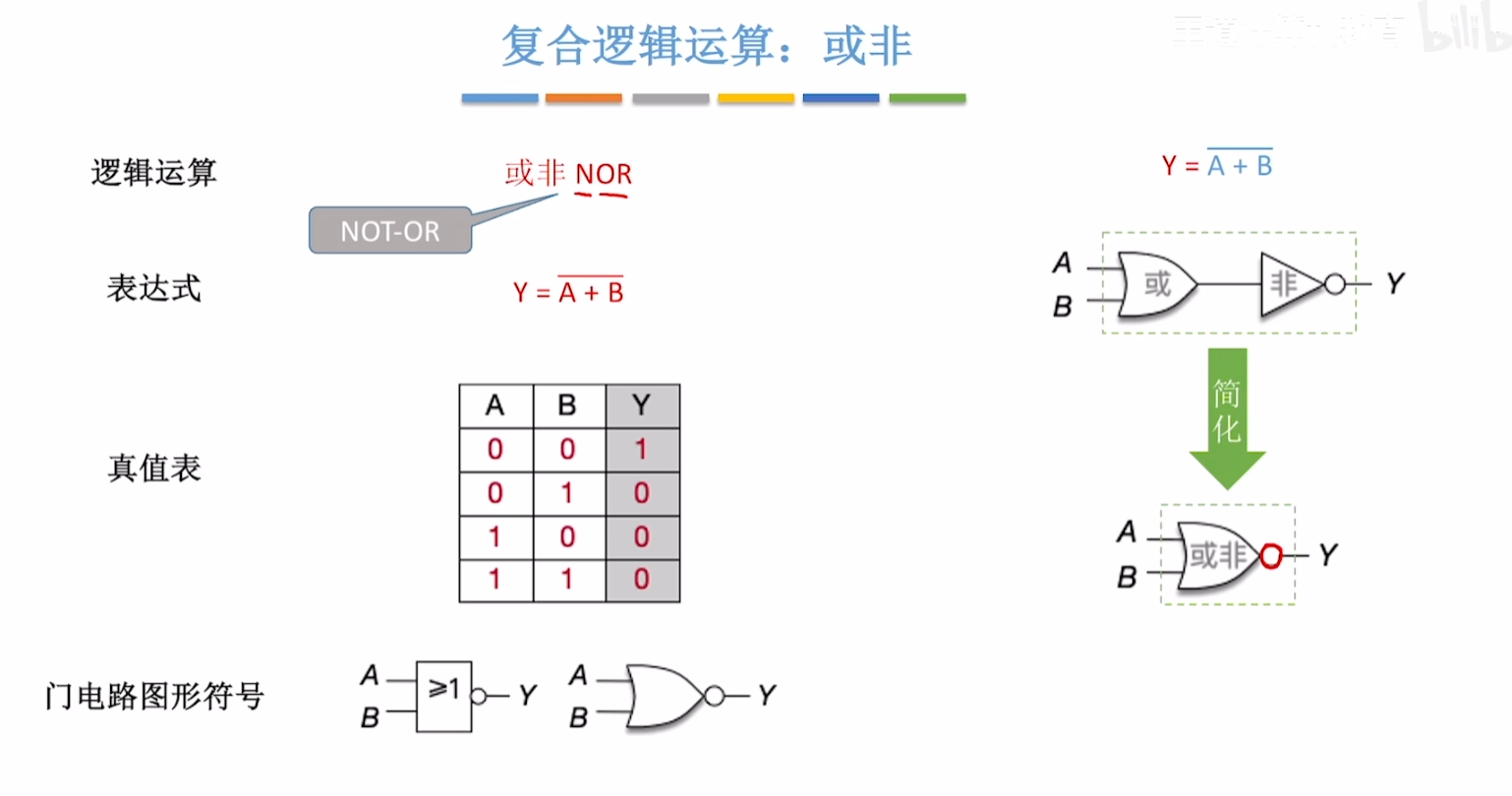

或非门

全 0 出 1

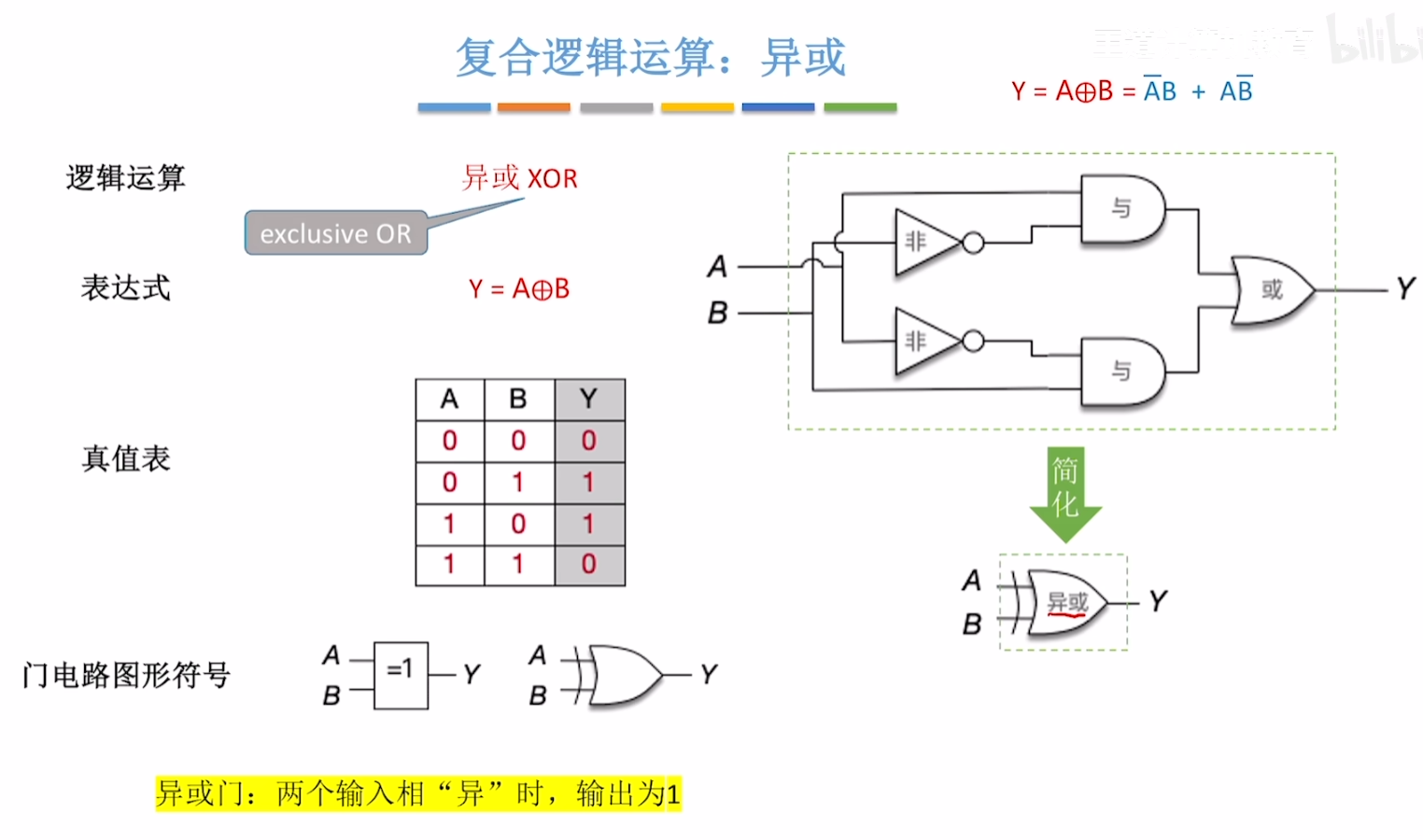

异或门

此处的简化做法体现了“封装” 的思想,即:屏蔽电路部件的内部实现细节,仅对外暴露出输入输出引脚,使用者仅需关心该部件的功能即可。

此处的简化做法体现了“封装” 的思想,即:屏蔽电路部件的内部实现细节,仅对外暴露出输入输出引脚,使用者仅需关心该部件的功能即可。

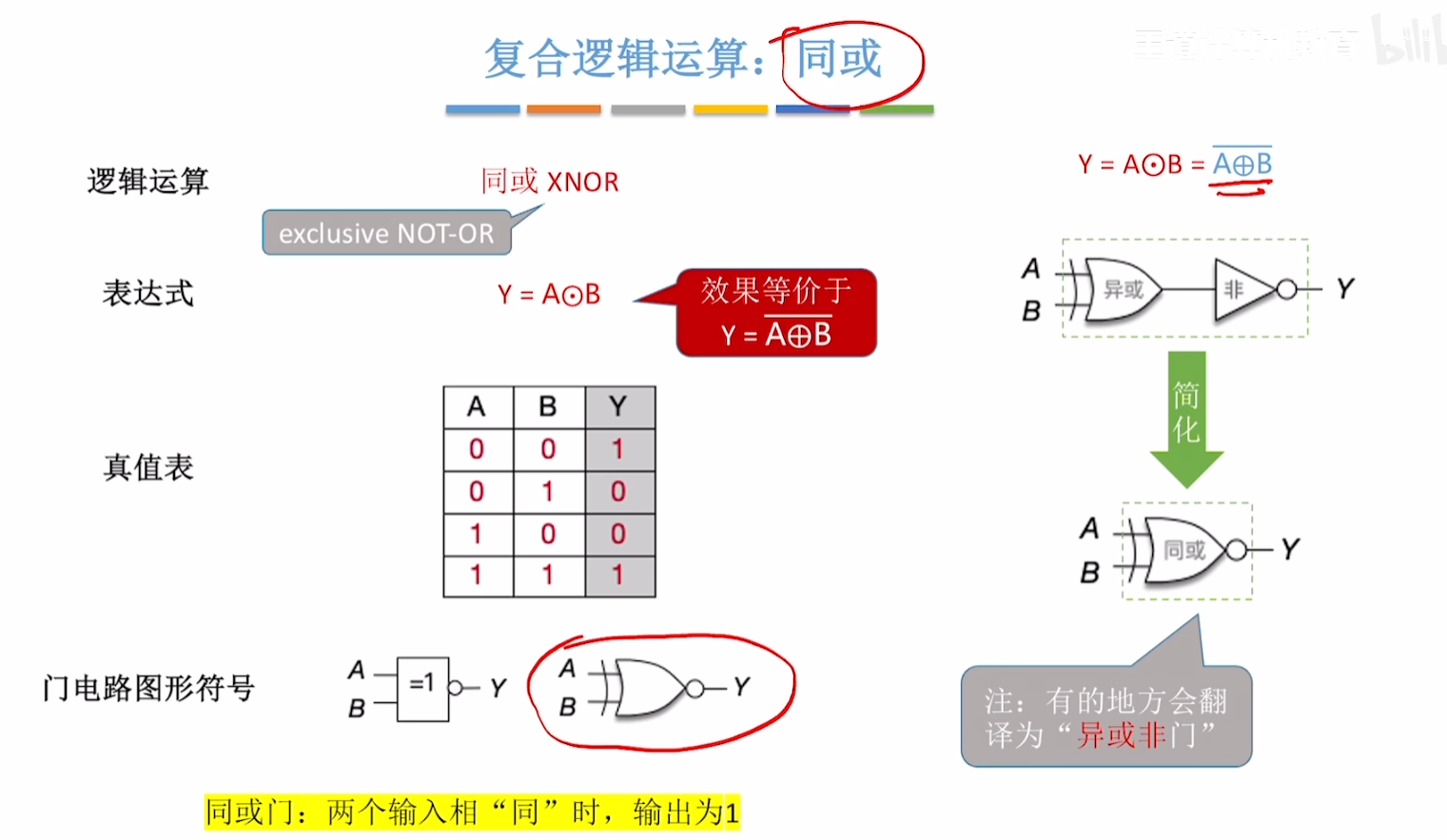

同或门

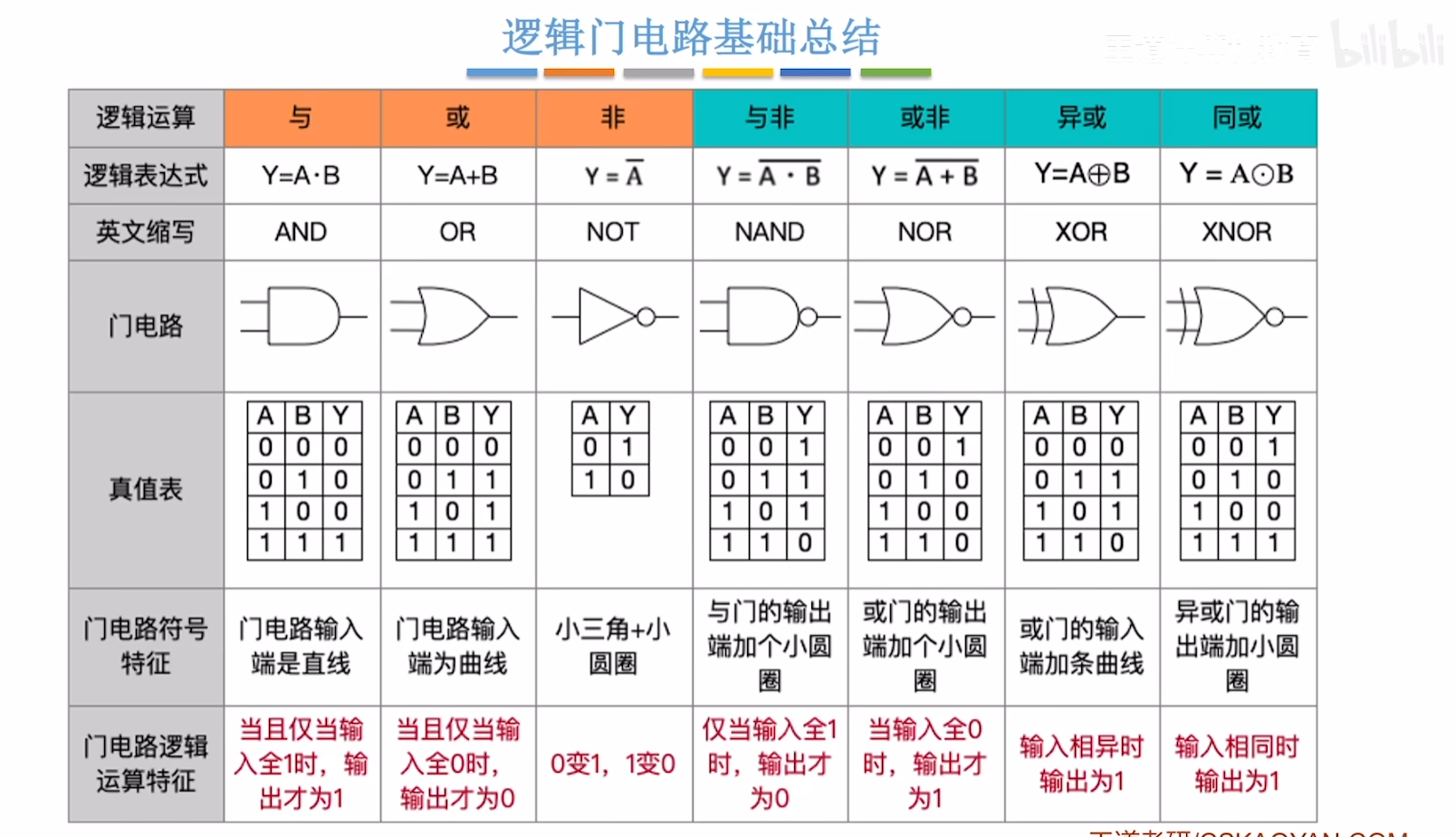

总结表单

需要关注各种门电路的画法,理解各种门电路逻辑运算的特征

需要关注各种门电路的画法,理解各种门电路逻辑运算的特征

补充

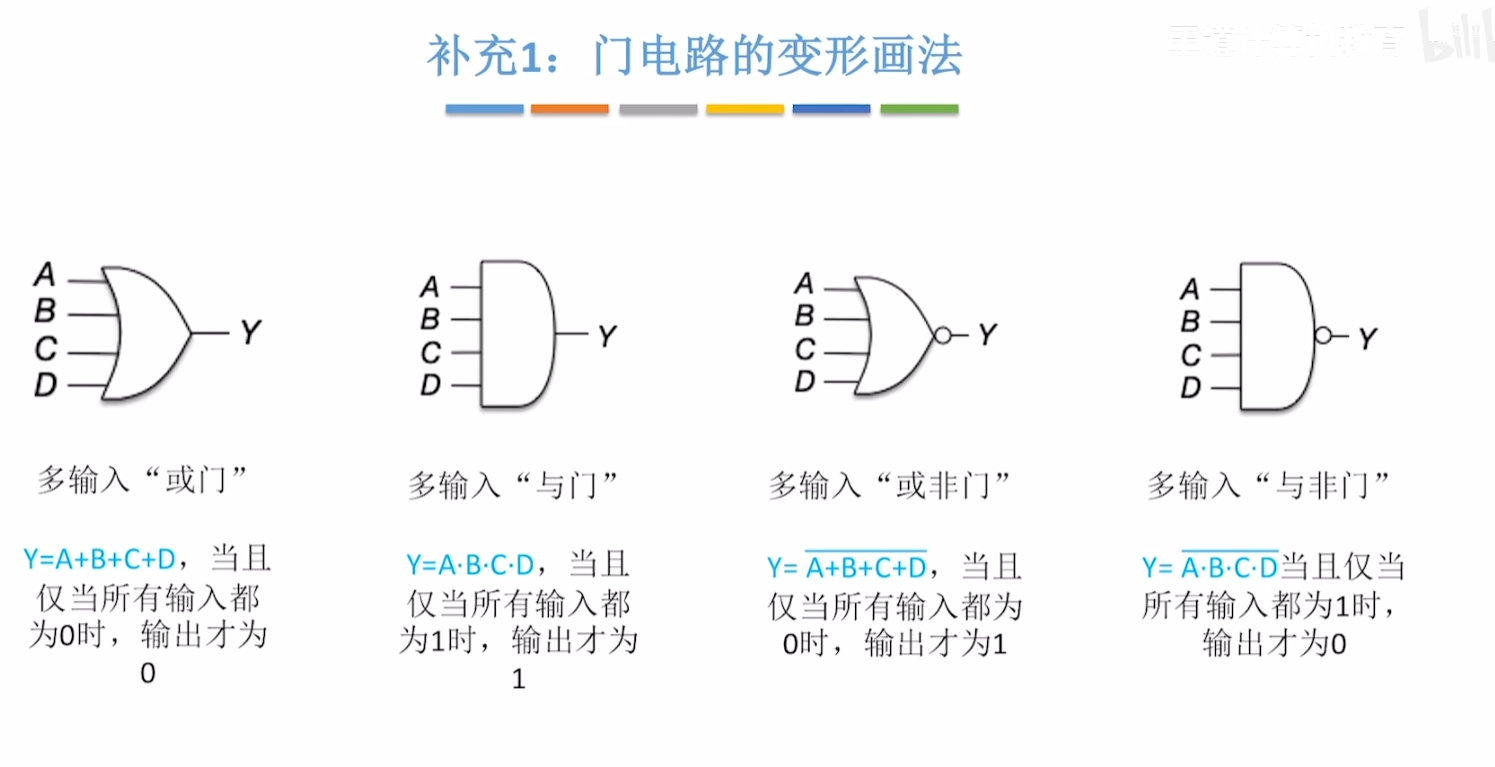

多输入画法

逻辑运算的优先级

优先级排序:非 > 与 > 或- 与、或可类比乘法和加法

- 如果有括号,则括号内的运算优先级更高

- 在非运算符下所有运算,可以理解为“隐含了一个括号”,即:

,即:需要先算括号内的值(非运算符底下的值)

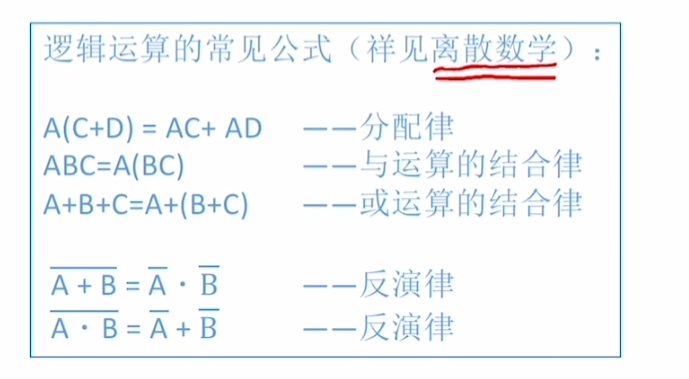

常见公式:

反演律也可称为

反演律也可称为

- 本质上,

逻辑表达式是对电路的数学化表示,简化逻辑表达式就是在简化电路设计,就是在省钱

拓展

用门电路设计电路,可实现二进制计算,而门电路是由"晶体管"实现的,若某芯片采用10nm制程,意味着该芯片内部的晶体管栅极宽度为10nm。

数字电路基础知识

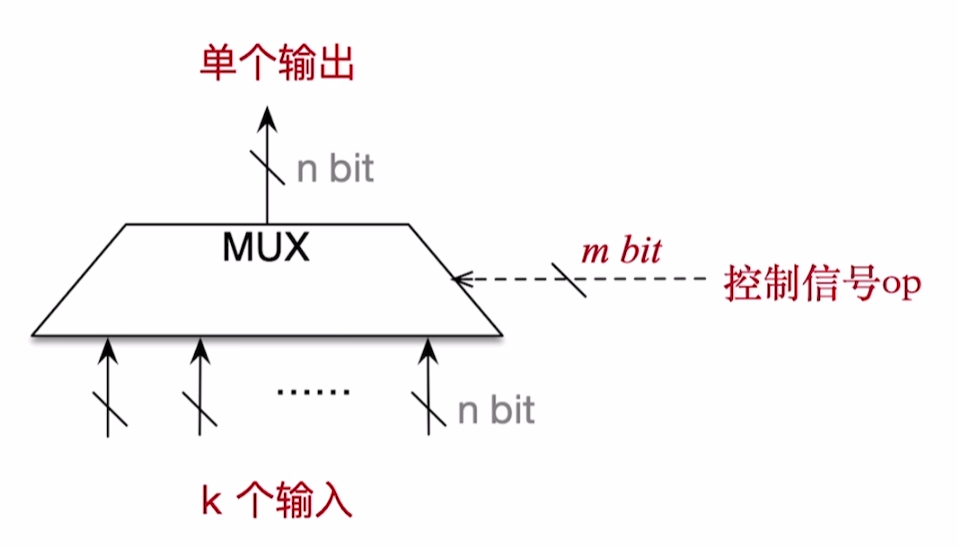

多路选择器(MUX)

- 作用:电路的“守门员”。在多个输入数据中,会根据控制信号op,只允许其中一个数据通过MUX

- 图形表示:通常用梯形表示,有多个输入,一个输出,一个控制信号 示例图:

- 若有 k 个输入,则控制信号的位数为:

,举个例子:若存在 8 个输入,编号为 0~7,则必须要有 个信号量来区分表示不同输入,故控制信号至少要有 3 位 - 控制信号常用 op 表示,一般用虚线表示

注

有的多路选择器可能会预留一个控制信号,来表示拦截所有输入,这时,取位数:

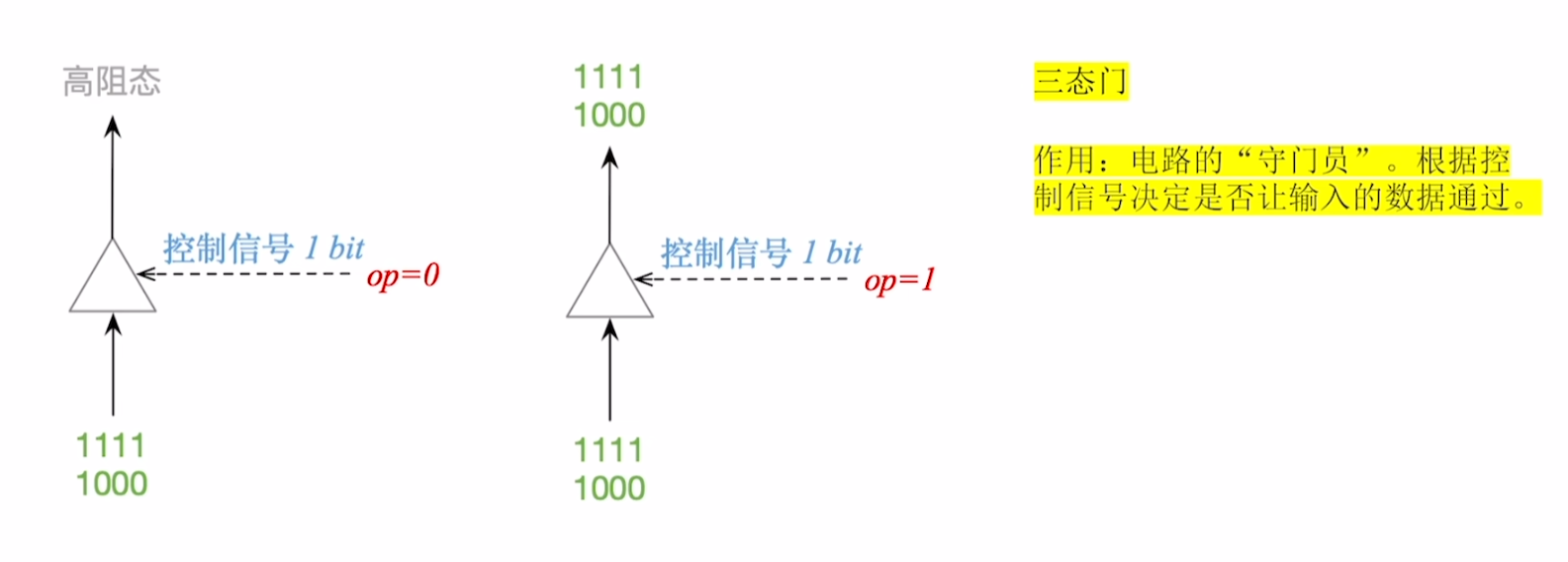

三态门

- 三态门只能决定是否让输入数据通过,若不让数据通过,则输出一个高阻态(若电路中使用0,1表示高低电平,高电平为5V,低电平为1V,则高组态是0V,即不属于高电平也不属于低电平)

- 三态门有控制信号,而非门没有控制信号